# An Amateur 900 MHz Spread-Spectrum Radio Design

Tom McDermott, N5EG, n5eg@tapr.org, Bob Stricklin, N5BRG, n5brg@tapr.org, Bill Reed, WD0ETZ, wd0etz@tapr.org

#### Abstract

System design principles and high-level design details are described for a new spreadspectrum radio design for the 900 MHz. Amateur band. The radio is designed to provide a 10-base-T interface as the data port, and is designed to provide transport of IP-based data. It is planned to provide both stand-alone and fully-networked hub configurations. The design is based on Frequency-Hopped Spread Spectrum (FHSS) spreading. Use of Forward Error Correction (FEC) and QPSK modulation should provide significant system gain performance compared to other FHSS FSK designs. The radio is currently in the printed-circuit board layout stage.

#### Introduction

Significant enhancement in the use and application of computer networking in the last 5 years has led to the need for high performance wireless interconnection of computers. Traditional 1200-baud and 9600-baud packet links are not able to provide adequate speed for today's web-based applications. Further, long-haul linking of multiple radios in linked configurations has proven difficult and unreliable. This can be seen from simple numerical analysis of the poor reliability of such multiple-hop configurations<sup>1</sup>. One solution to the reliability issue is to utilize other transport facilities for most of the transmission distance, such as the Internet.

In industry, wireless is valued greatly for the ability to provide mobility. Thus, fiber optics has replaced radio in the long-haul telephony networks (for most, but not all applications), and wireless is increasingly looked upon as a replacement for the wire copper loop. This inverts the traditional view of the wired and wireless domains<sup>2</sup>.

## Applications

A high-speed mobile data access infrastructure to the Internet has many applications for the radio amateur, and could allow the provision of services and applications not possible with current commercial technologies. This is especially true as the Internet performance improves to support constant-bit rate multimedia services. Current audio coding technology provides quite acceptable audio at 13 kb/s. Videoconferencing is reasonably acceptable at 112 kb/s. Web browsing is possible at any speed, but only tolerable above 28 kb/s. A wireless interconnection technology that could support data rates in this range would provide the ability for the radio amateur to provide audio conferencing, via the Internet, from a mobile laptop computer to anywhere in the world in real time. Mobile laptop videoconferencing is similarly possible. Access to databases, maps, Email, etc., anywhere on the Internet in real

time would make the utility of such a service very great. The radio amateur, equipped with such a capability could prove invaluable in many public-service scenarios. Indeed, the Internet not only addresses many of the problems of previous-generation packet networking, in fact it provides a powerful tool in its almost universal accessibility and rich diversity of information.

### System Requirements

The design of a radio to meet the above applications is described. The general requirements are that the radio provide at least 128 kb/s throughput (more in other modes) while providing 20-mile coverage with 1-watt output power. 10-base-T was selected as the desired interface, and it is intended for connection to the LAN port of a laptop or other computer. It is envisaged that both a point-to-point configuration and a hubbed multi-point configuration would be supported. In the point-to-point configuration the radios would simply provide a transparent LAN interconnection pipe. For example, one radio might be connected to an Internet service, and located on top of a tall building, while the other end would be connected to a mobile laptop computer.

In the multi-point configuration, several radios are placed at a common site, such as a tall building. One channel becomes the control channel, and each of the remaining radios serves as a data channel. This provides for multiple users to simultaneously access the hub site. In the hub mode, all radios transmit and receive in synchronism. Additionally, good Internet connectivity might not be available at such a hub site, so individual data channels of the hub can be dedicated as fixed point-to-point links that provide a remote link to the Internet from the hub site. The radio design supports these configurations automatically with additional hardware. The control channel allocates access to idle data channels.

In the hub mode, the hub provides for dynamic assignment of IP addresses to the user computers via the DHCP protocol. This eliminates many of the difficulties of IP address administration in a mobile environment. However, it does not allow the user to move the computer from one node to another while connected. Instead the link will be broken and will have to be re-established with a new IP address.

## Spreading Methods

Both Direct-Sequence Spread Spectrum (DSSS) and FHSS were studied. The Harris Prism<sup>™</sup> chipset was initially investigated for such a radio. This chipset is designed to provide 802.11 wireless LAN for mobile laptop computers. However, this excellent chipset cannot easily provide the required system gain and performance required for a 20-mile link. It was intended to provide a low-cost low-power 1 Mb/s LAN interconnection primarily within a few 100's of feet. The Prism chipset utilizes DSSS modulation, and provides a spreading gain of only 12 dB. maximum, 11 dB typically. Further it is designed for the 2.4 GHz. band, which we felt would be difficult for average amateurs to equip with adequate antennas and feedline to meet the link distance requirement. We chose to implement the first radio design in the 900

MHz. Amateur band (902-928 MHz., a width of 26 MHz.) due to the availability of commercial components.

At first blush 20 dB of system gain (100:1 spreading ratio) within a 26 MHz wide band implies a maximum data rate of 26/(100\*2) = 130,000 b/s. Since we also wanted the radios to operate half-duplex (to minimize cost), this maximum rate would be further reduced to 65,000 b/s. The data rate could be doubled if QPSK modulation is utilized, because it halves the spectral requirements. However, we noted in several spectrum analyzer sweeps of the 900 MHz band in Dallas, Texas that a large number of very strong narrow-band carriers are present. Testing with commercial part-15 radios indicated that these strong carriers render DSSS radios inoperative when the link distance was increased beyond one or two miles.

However, tests with FHSS radios under the same conditions proved to be more encouraging. Eventually, 20-mile links were achieved with one FHSS radio when the antennas were converted to horizontal polarization. Horizontal polarization reduced the amplitude of the interfering carriers by more than 20 dB. Thus an FHSS-based radio design was selected.

## System Design Parameters

The parameters that were initially selected for the radio design are based on the availability of off-the-shelf SAW filters for the IF strip, what we felt was an achievable settling time for the frequency hopping VCO, available integrated circuits, and an aggressive but hopefully reasonable demodulator synchronization time. These parameters have been selected as follows:

| Dwell time on each slot:     | 10 milliseconds                          |  |

|------------------------------|------------------------------------------|--|

| IF filter bandwidth:         | 600 kHz.                                 |  |

| RF instantaneous bandwidth:  | 600 kHz.                                 |  |

| RF channel bandwidth:        | 26 MHz.                                  |  |

| Number of slots within band: | 43                                       |  |

| Modulation format:           | QPSK, square-root raised-cosine roll-off |  |

| Forward Error Correction:    | Convolutional, based on K=7 coder and    |  |

|                              | Viterbi decoder. Code rate = 1/2 or 7/8  |  |

|                              | depending on mode.                       |  |

| Frame structure:             | Based on HDLC frame                      |  |

| Demodulator:                 | Digital Costas-loop design               |  |

| Modulation rate (all modes): | 300 kilo-symbols/second                  |  |

| Transmit / Receive mode:     | Time-Division Half-Duplex                |  |

| Data throughput (mode 0):    | 150 kb/s (minus overhead)                |  |

| Data throughput (mode 1):    | 300 kb/s (minus overhead)                |  |

| Data throughput (mode 2):    | ~525 kb/s (minus overhead)               |  |

Table 1 indicates the modes of operation that are anticipated.

The use of FEC and QPSK provides at least 9 dB improvement in system gain as compared to uncoded non-orthogonal Frequency-Shift Keying (FSK) which is utilized in almost all commercial part-15 radios. However, the use of coherent modulation techniques increases both the cost of the radio and the difficulty of the design. We felt the 9 dB. performance improvement made this tradeoff worthwhile. Fortunately, Harris provides a DSP-based digital Costas-loop QPSK demodulator IC (the HSP 50210) which appears to have sufficient programmability to meet the synchronization speeds provided that some clever algorithms ("quick-lock") are employed.

Two risks are felt to represent the greatest challenges in the radio design. First is the ability of the hopping VCOS to settle to adequate frequency accuracy and stability within 10 milliseconds. Second is the ability of the Digital QPSK loop demodulator to achieve synchronization lock with our special "quick-lock" technique. The prototype design will be used to assess these design risks.

#### Block Diagram

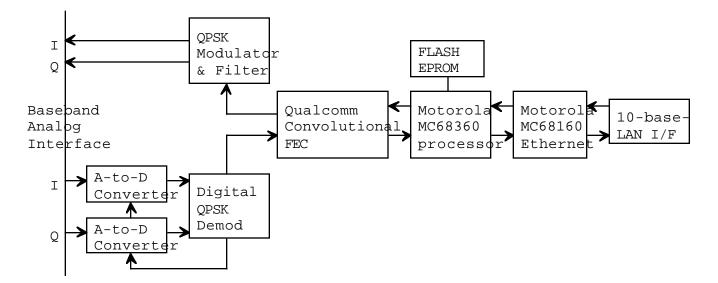

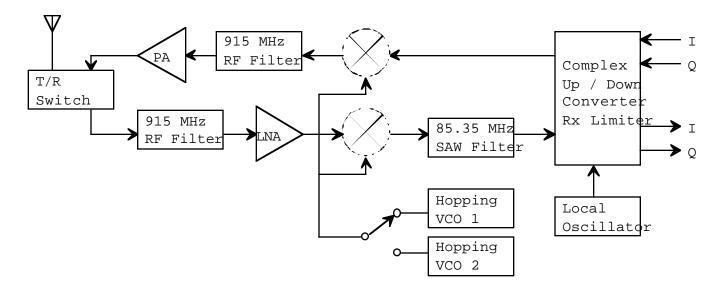

Figure 1 is a block diagram of the baseband processing, processor, and LAN Interface portions of the radio. Figure 2 is a block diagram of the RF and IF processing parts of the radio. The radio design is based on a Motorola 68360 microprocessor. It controls all major functions of the radio, and the LAN interface. A Motorola 68160 provides the 10-base-T Ethernet port. FLASH memory is utilized solely in the processor, to allow updates of the code at a later time without physically opening the radio or removing / programming any EPROMS.

Figure 1 – Block Diagram: Baseband Processing and LAN Interface

#### **Circuit Description - Transmit Direction**

The data from the LAN port is buffered by the 68360 and converted to a proprietary frame format based on HDLC and then sent to a Qualcomm convolutional coder IC. In modes 0 and 1, the coder produces two output bits for each input bit (rate = 1/2 mode). In mode 2, the code is punctured to rate = 7/8. These two bits become the in-phase (I-) and quadrature (Q-) channels to a Motorola QPSK modulator IC. The modulator IC provides raised-cosine roll-off at baseband of the two channels via an FIR filter. It also contains two D-to-A converters, and thus provides the I- and Q- analog baseband output signals.

The two baseband analog signal are connected to a Harris quadrature up-converter IC that generates I- and Q- signals at the IF frequency of 85.35 MHz. These signals are then further upconverted to the 902 MHz band, and filtered by a dielectric filter to eliminate the IF image frequency. It is then amplified by a Motorola integrated PA chip to about 100 milliwatts. The signal is routed through a PIN diode switch and through a pair of directional couplers to the antenna connector. The directional coupler signals are rectified and filtered, and fed to an A-to-D converter chip. These signals provide measurement of the forward and reflected power levels.

Figure 2 – Block Diagram: RF and IF processing

### **Circuit Description - Receive Direction**

In the receive direction, the signals are passed through a dielectric filter (to eliminate the image frequency) and then to a Motorola low-noise downconverter IC. From there they pass through an 85.5 MHz, 600 kHz wide SAW filter and an amplifier. At that point, they are sent to a Harris downconverter IC which provides a large amount of gain through a two-stage limiter, and then downconverts the signal to baseband, producing the I- and Q- baseband analog signals. These signals are then digitized by a pair of 10-bit A-to-D converters, and sent to the Harris digital Costas-loop demodulator IC.

The demodulator IC first performs a complex frequency rotation to adjust for any frequency offset and phase error between the transmitter and receiver, then provides symbol timing and carrier frequency acquisition and tracking. Finally it provides AGC on the demodulated baseband signals, and performs a soft-decision threshold comparison of the I- and Q- channels against the reference level. These are in the form of two 3-bit words, one for the I- channel, and one for the Q-channel.

The pair of I- and Q- soft decision signals are sent to the Qualcomm Viterbi decoder IC. Is it capable of determining the synchronization boundary of the QPSK symbols, and decoding the FEC algorithm. The decoded bits (at one half the rate of the input bits in modes 0 and 1) are then sent to the HDLC portion of the Motorola 68360. The microprocessor recovers and removes the HDLC frame, and transmits the received data out the 10-base-T LAN port via the 68160.

## Hopping VCOS

The design utilizes two VCOS in a pair of phase-locked loops (PLLS). While one loop is operational on frequency, the other loop is busy slewing to a new frequency. At the end of each 10-millisecond period, the new VCO becomes the active VCO and the previously active VCO is slewed to another channel. In this manner, each VCO plays leapfrog, being utilized half the time. This allows each phase locked loop 10 milliseconds to achieve satisfactory frequency accuracy before it is switched into service.

All of the RF-determining reference frequencies are derived from a single crystal-controlled oscillator. This oscillator is ovenized to minimize its error from the desired frequency during temperature excursions.

The actual programming of the VCO PLLS occurs by a small PIC chip (one-time programmable single chip processor). This chip contains the hopping sequence of the radios, and cannot be altered by the user. United States Department of Commerce regulations prohibit the export of FHSS radios from the United States if the hopping sequence can be altered by the user.

## Synchronization

The most difficult part of any design is the synchronization of the transmitter and receiver, both in terms of the Transmit / Receive switching (T/R) and also in terms of carrier frequency acquisition. An initial synchronization interval occurs prior to the radios becoming linked. This takes some time to occur. The demodulator utilizes a sweeping process to recover carrier lock. However once this is achieved, the microprocessor is capable of reading out the frequency error at the receiver demodulator from the acquisition register in the demodulator. Based on the actual RF channel utilized during the initial synchronization, it computes the master-oscillator frequency difference between the transmitter and receiver. Subsequently, each time that the radio hops channels, the microprocessor computes the new effective frequency difference, and pre-loads the demodulator carrier recovery loop register with the proper frequency offset value to place the recovered carrier very close to the proper frequency. This helps the demodulator lock very quickly. This is the "quick-lock" technique referred to earlier.

#### Acknowledgements

We would like to thank the Tucson Amateur Packet Radio Corporation (TAPR), which is sponsoring this project.

Copyright 1997 TAPR.

| Mode | End Points                                                                                  | Performance                                                                                                                                                                              | Throughput |

|------|---------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| PPS  | Point-to-point search                                                                       | Search mode to establish initial link in PP mode.                                                                                                                                        |            |

| PP0  | Point-to-point (i.e.<br>user end system to<br>user end system)                              | Rate=1/2, half-duplex, 10 msec<br>T then 10 msec R.                                                                                                                                      | 150 kb/s   |

| PP1  | Point-to-point (i.e.<br>user end system to<br>user end system)                              | Rate=1/2, transmit slots as needed, communication of slot requests across link.                                                                                                          | 300 kb/s   |

| PP2  | Point-to-point (i.e.<br>user end system to<br>user end system)                              | Rate=7/8, transmit slots as needed, communication of slot requests across link.                                                                                                          | 525 kb/s   |

| PNS  | Point-to-Control Link<br>(i.e. user end system<br>to control link of a<br>multi-radio node) | Search mode to establish initial link to control channel of a node.                                                                                                                      |            |

| PN0  | Point-to-Node (i.e.<br>user end system to<br>data channel of a<br>node).                    | Rate=1/2, half-duplex, 10 msec<br>T then 10 msec R.                                                                                                                                      | 150 kb/s   |

| PN1  | Point-to-Node (i.e.<br>user end system to<br>data channel of a<br>node).                    | Rate=1/2, transmit slots as<br>needed, communication of slot<br>requests across link, with node<br>doing slot voting across all<br>channels and downstream<br>notification to all users. | 300 kb/s   |

| PN2  | Point-to-Node (i.e.<br>user end system to<br>data channel of a<br>node).                    | Rate=7/8, transmit slots as<br>needed, communication of slot<br>requests across link, with node<br>doing slot voting across all<br>channels and downstream<br>notification to all users. | 525 kb/s   |

# Table 1 – Proposed Operational Modes

<sup>&</sup>lt;sup>1</sup> A Primer on Reliability as Applied to Amateur Radio Packet Networks, T.C. McDermott, N5EG, 13<sup>th</sup> ARRL Digital Communications Conference proceedings, pp. 122-125

<sup>&</sup>lt;sup>2</sup> This effect has sometimes been called the "Negroponte Inversion", after Nicholas Negroponte.